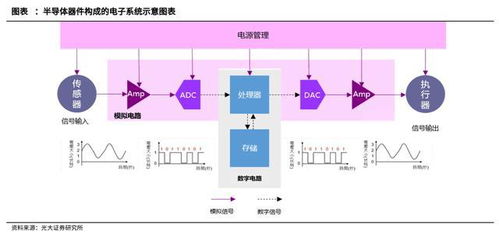

運算放大器(Op-Amp)和比較器(Comparator)是兩種在模擬集成電路設計中極為常見且功能強大的器件。它們在電路符號上相似,內部結構也有重疊之處,例如都包含高增益的差分輸入級。它們的核心設計目標、工作原理、性能指標和應用場景存在根本性的區別,理解這些差異對于正確選擇和設計電路至關重要。

1. 核心功能與設計目標

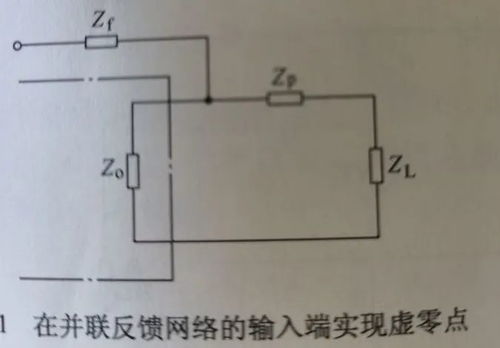

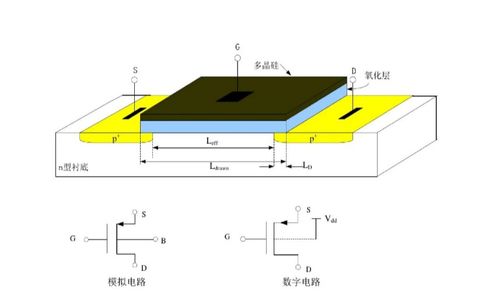

- 運算放大器:其設計目標是實現一個高增益、高線性度的電壓放大器。在負反饋配置下(如反相、同相放大器),其輸出與輸入之間呈現精確、穩定的線性關系。運算放大器的“理想”狀態是虛短(輸入電壓差趨于零)和虛斷(輸入電流趨于零),其開環增益越高,閉環線性度越好。

- 比較器:其設計目標是快速、準確地比較兩個模擬電壓的大小,并輸出一個明確的高低電平(數字邏輯信號)。它工作在開環或正反饋(遲滯比較器)狀態,其輸出在輸入電壓差跨越閾值時發生“翻轉”,旨在實現模擬到數字的轉換。

2. 內部結構的關鍵設計差異

- 輸出級:這是兩者最顯著的結構差異。

- 運算放大器:通常采用推挽輸出級,能夠雙向(源電流和吸電流)驅動阻性負載,并設計為在負反饋下穩定工作,避免輸出飽和。其壓擺率(Slew Rate)和帶寬需平衡,以確保線性放大時的信號保真度。

- 比較器:輸出級通常是開漏(Open-Drain)或推挽數字輸出,旨在快速驅動數字邏輯門(如CMOS、TTL電平)。為了追求極快的翻轉速度,比較器通常不內置頻率補償電容,這使其在負反饋下極易振蕩。其壓擺率是核心指標,要求盡可能高。

- 響應速度與穩定性:

- 運算放大器:通過內部頻率補償(如米勒補償)來確保在任何閉環增益下的穩定性,但這犧牲了帶寬和壓擺率。其建立時間(Settling Time)是關鍵指標。

- 比較器:不進行內部頻率補償,從而獲得極高的響應速度。其關鍵指標是傳播延遲(Propagation Delay),即從輸入過閾值到輸出完成翻轉的時間。

- 輸入失調電壓:兩者都追求低失調,但對比較器而言,失調電壓直接影響比較精度和閾值準確性,在高速比較器中需特別優化。

3. 性能指標側重點

- 運算放大器重點指標:開環增益、增益帶寬積(GBW)、壓擺率、建立時間、輸入失調電壓與漂移、共模抑制比(CMRR)、電源抑制比(PSRR)、噪聲等。

- 比較器重點指標:傳播延遲、壓擺率、輸入失調電壓、遲滯(可內置或外設)、輸出電平兼容性、最小過驅動電壓下的響應時間等。

4. 應用場景與使用禁忌

- 運算放大器典型應用:模擬信號放大、濾波(有源濾波器)、數學運算(加、減、積分、微分)、精密電壓基準、模擬伺服控制等線性電路。

- 比較器典型應用:模數轉換(ADC)的前端、電壓監測與門限檢測、方波/脈沖波生成、波形整形、數字接口電平等非線性開關電路。

- 重要禁忌:

- 切勿將比較器當作運放用于閉環線性放大。由于其無內部補償,接入負反饋會產生嚴重振蕩。

- 通常不建議將運放當作比較器使用。當運放開環工作時,其輸出飽和到電源軌的速度較慢(壓擺率低),且飽和恢復時間長。其輸出電平可能不符合數字邏輯要求,傳播延遲也遠大于專用比較器。僅在速度、精度要求極低的場合可勉強替代。

5. 集成電路設計考量

在芯片設計層面,設計師會根據上述不同目標進行優化:

- 對于精密運放,會采用復雜的電路結構(如自動歸零、斬波穩定)來抑制失調和漂移,精心設計補償網絡以保證穩定性。

- 對于高速比較器,會采用鎖存(Latch)結構、預放大器鏈來最小化傳播延遲,并優化輸出級以實現與數字電路的無縫連接。

###

簡而言之,運算放大器是為“放大”而生,追求線性與穩定;比較器是為“判決”而生,追求速度與明確。在集成電路設計中,選擇正確的器件并理解其底層設計哲學,是確保系統性能、可靠性和成本優化的關鍵一步。混淆二者的使用,往往是電路失效或性能不佳的常見根源。